Delay slots are an artifact of some early pipelined architectures in which pipeline hazards were not handled explicitly. The algorithm works by building an approximate cfg and then refining it to reflect the actions of delayedbranches.

Nice Bonuses On 5 Bet Triple Fortune Dragons Unleashed Quil Ceda Creek Casino Wa Lagu Mp3 - Mp3 Dragon

The branch delay slot is a dynamic concept.

Branch delay slots assembly. 2 (b) which instruction(s) in the assembly sequences below would you place in the delay slot(s), assuming Otherwise, the sequence of instructions executed when the delayed. When target is another branch • philosophically, delay slots good?

On the mips architecture, jump and branch instructions have a delay slot. Instead of addressing each comment, i’ll just make a post out of it. The delay slot is a way to recover one product from having to be discarded in the line.

If all branches have explicit targets, the complexity of the refining step is linear with respect to the number of branches in the code. Practice using one of our 50 free blackjack games now before playing blackjack for real money. Branch delay slots are one of the awkward features of risc architectures.

Step through the code and watch $8 (count) increase from 0 to 0xa. There seems to be a lot of confusion over branch delay slots. Instead of n products coming out before the line stopped, n+1 products came out per production run.

(a) what is the number of delay slots needed to ensure correct operation? The next line of code following the jump/branch will always be executed along with the jump/branch. Risc cpus are pipelined by definition, so while the current instruction is in execution, the following instruction (s) will be in the pipeline already.

I was puzzled for while by some unexpected assembly produced by gcc while working on my own implementation of the mips isa, further investigation yielded the following results about the branch delay and the load delay slots, both of them occurred in early mips architectures. The mips r4000, part 11: The instruction following the branch is executed before the branch takes effect.

This means that the instruction after the jump or branch instruction is executed before the jump or branch is executed. You are unable to find any instructions to fill the delay slot. Having fun with branch delay slots.

Instruction slots following branches are known as branch delay slots. The processor has two delay slots and the two instructions following the branch are always fetched and executed, and. It is there as a convenient target for the branch instruction.

More on branch delay slots. Machine uses delay slots to handle control dependences. Delay slots can also appear following load instructions;

If a branch or call is done on a sparc, the new address is loaded into the npc, not the pc. Rect cfgsfromscheduled assembly code that includes branches in branch delay slots. If there is for example a conditional branch in the.

We show how to transform the assembly language to a form which has no delay slots. The position immediately following any branch or call instruction is called the delay slot, and the instruction in that position is the delay instruction. These are defined load delay slots.

A human must remember that the control transfer Spend a few minutes learning blackjack rules, and new players can easily progress to branch delay slots assembly making smart blackjack bets quickly. With a few assembly language directives, the code is ready to run.

When branches are processed by a pipeline simply, after each taken branch, at least one cycle remains unutilized. I change cpu0 backend to a 5 stages of classical risc pipeline machine with one delay slot like some of mips model (the original cpu0 from its author, is a 3 stages of risc machine). In addition, there is a group of branch likely conditional branch instructions in which the instruction in the delay.

That is like what happens with a branch, somewhere deep in the assembly line, something causes the line to have to change, dump the line. With this change, the backend needs filling the nop instruction in the branch delay slot. From this form, we can.

Jump targets, branch targets and destinations are resolved in the execute stage. When a branch instruction is involved, the location of the following delay slot instruction in the pipeline may be called a branch delay slot.branch delay slots are found mainly in dsp architectures and older risc architectures.

Online Casinos Slot Machines Blog Archive Triple Fortune Dragon Slot Review

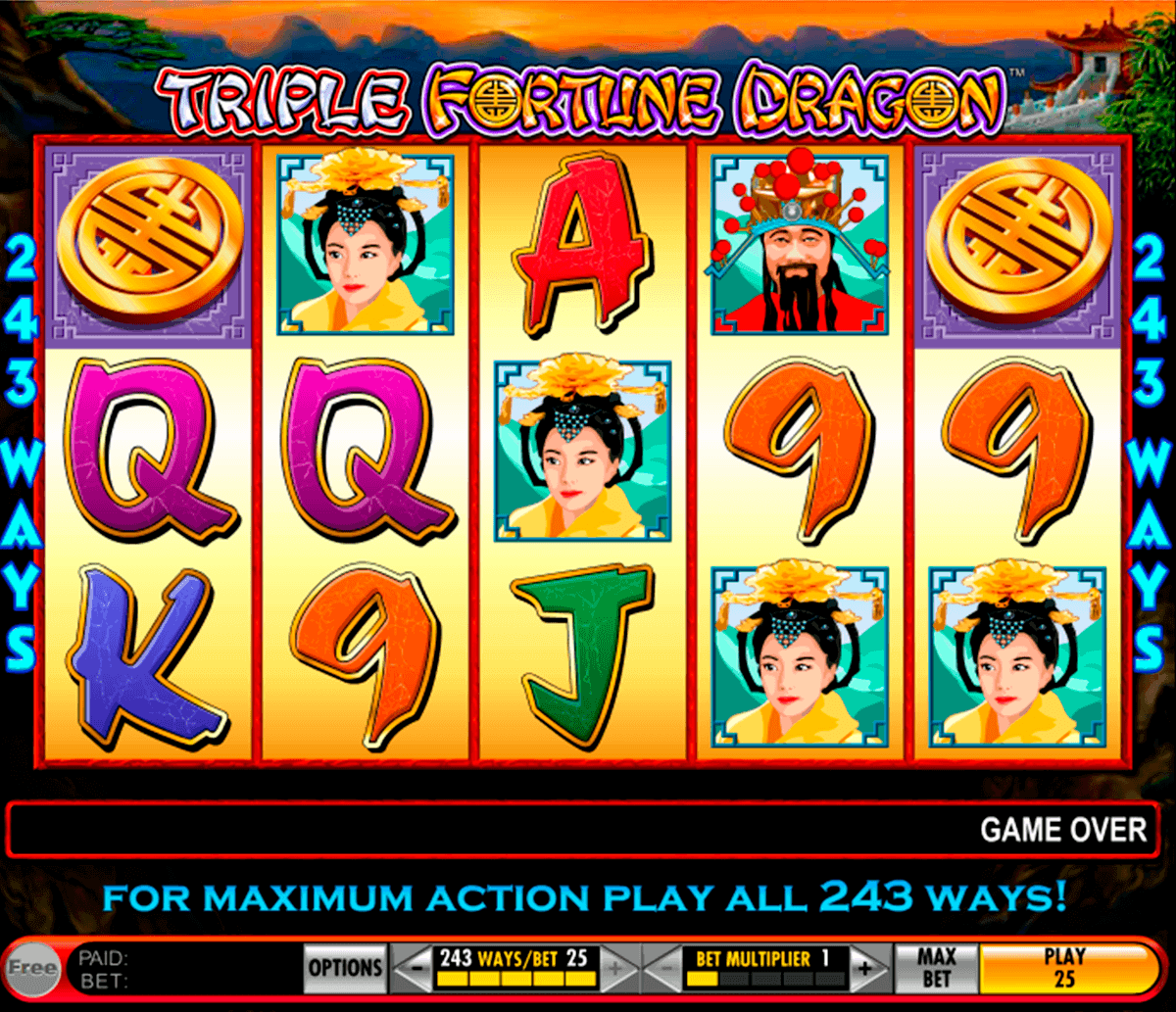

Triple Fortune Dragon Slot Slot Machines Online

Triple Fortune Dragon Slot Machine Download Pc Free

Play Triple Fortune Dragon Free Slot Igt Casino Slots Online

Triple Fortune Dragon Slot Machine Download Pc Free

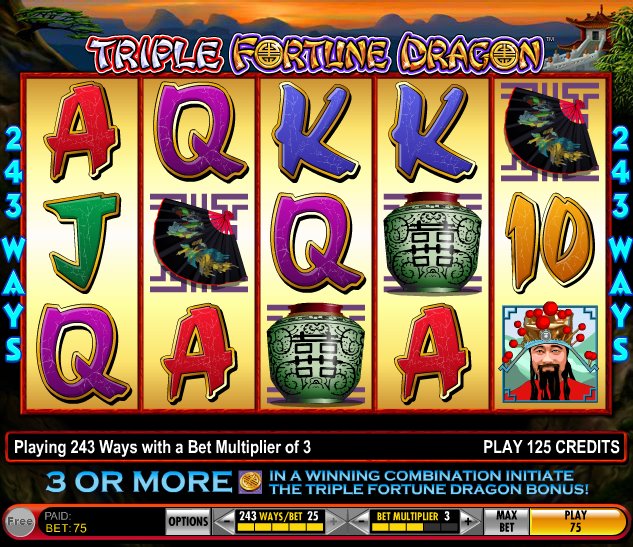

Triple Fortune Dragon Slot Review Money-making Casino Apps

Triple Fortune Dragon 243 Ways Example - 243wayslotscom243wayslotscom

Triple Fortune Dragon Slot Review Live Dealer Casino Sites

Triple Fortune Dragon Slot Slot Machines Online

Triple Fortune Dragon Slot -- Renowned Game Websites

17 Mb 2 Jackpots With The Same Pattern Download Lagu Mp3 Gratis - Mp3 Dragon

Triple Fortune Dragon Igt Slots Play For Free Real Ipad Or Iphone

Triple Fortune Dragon Slot Machine - Youtube

Triple Fortune Dragon - Free To Play Igt Slot Machines

Triple Fortune Dragon Slot Slot Machines Online

Triple Fortune Dragon Slots Review Find Slot Machine Games

17 Mb 2 Jackpots With The Same Pattern Download Lagu Mp3 Gratis - Mp3 Dragon

Triple Fortune Dragon Slot Machine Download Pc Free

0 comments